一文看懂晶圓廠相關的工藝、技術和其他

摘要:本文詳細為大家介紹整個晶圓廠的現狀,其中也包括對晶圓相關的專業名詞以及一些基本概念的介紹和普及。

基本概念科普

什么是納米(nm)

這是一個單位,也就是1米的十億分之一。用一個指甲來作比喻的話,那就是說試著把一片指甲的側面切成10 萬條線,每條線就約等同于1 納米,由此可略為想像得到1 納米是何等的微小了。

圖1

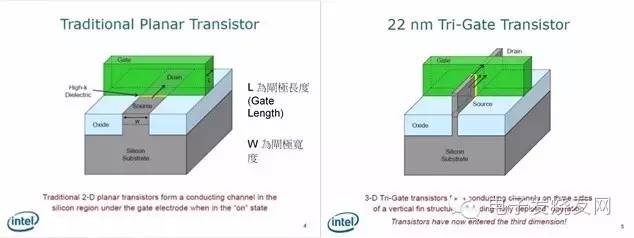

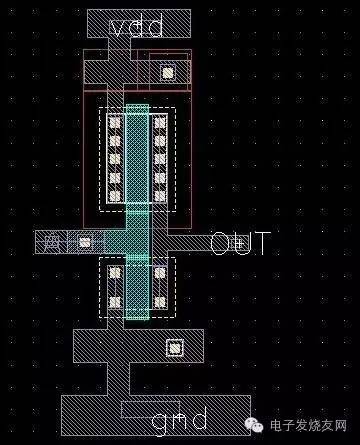

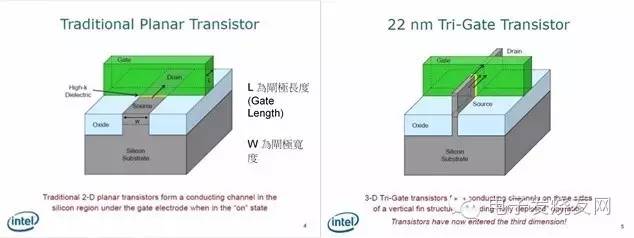

拿現在最常被提到的14nm制程來說,這里所指14nm的,是指在芯片中,線最小可以做到14納米的尺寸,下圖為傳統電晶體的長相,以此作為例子。縮小電晶體的最主要目的就是為了要減少耗電量,然而要縮小哪個部分才能達到這個目的?左下圖中的L就是我們期望縮小的部分。藉由縮小閘極長度,電流可以用更短的路徑從Drain端到Source端。

拿現在最常被提到的14nm制程來說,這里所指14nm的,是指在芯片中,線最小可以做到14納米的尺寸,下圖為傳統晶體管的長相,以此作為例子。縮小晶體管的最主要目的就是為了要減少耗電量,然而要縮小哪個部分才能達到這個目的?左下圖中的L就是我們期望縮小的部分。藉由縮小閘極長度,電流可以用更短的路徑從Drain端到Source端。

圖2

還是看不懂?沒關系,我們再來點具體的介紹。

看看知乎網友郭二是怎么解析的:

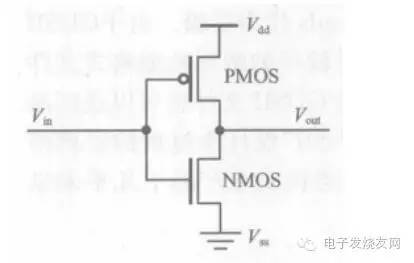

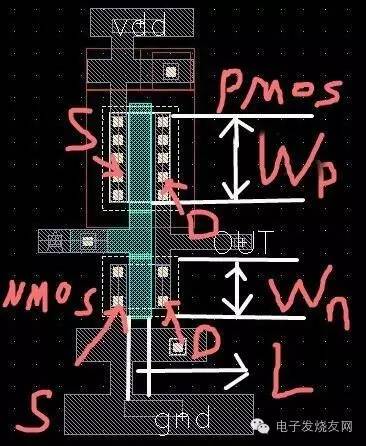

用一個反相器的圖來說明一下。

圖3

從圖3我們可以看出:

PMOS接Vdd的一端是源端S(p),接輸出的一端是D(p),接Vin的是柵端G(p)。

NMOS接Vss的一端是源端S(n),接輸出的一端是D(s),接Vin的是柵端G(s)。

圖4

下面這兩張圖是CMOS反相器的版圖,即俯視圖。一張沒有做標記,一張做了標記。電路圖是做設計時的一種抽象的符號,而版圖則是在工廠生產電路的時候,需要的投影模板的形狀,所以它必須是俯視圖。集成電路的生產是在硅片上不斷用各種形狀的掩膜版遮擋住不要被光線曝光的部分,來進行生產的(具體細節找本工藝書或者集成電路的書都會有粗略的介紹)。

圖5

做標記的圖中,上邊是PMOS,下邊是NMOS,連接兩個MOS管的是多晶硅,數字電路一般硅的長度L是固定的,取工藝最小值,比如你選擇的工業是28nm,那么L=28nm,而Wp和Wn則是設計標準單元的工程師可以調節的參數,用來追求某些指標,比如面積要小,驅動能力要強,延遲要小等等。那么這個L就是指PMOS管和NMOS管中,有源區之間的距離,即源區(S)和漏區(D)之間的距離。具體在下文中還有介紹。

圖6

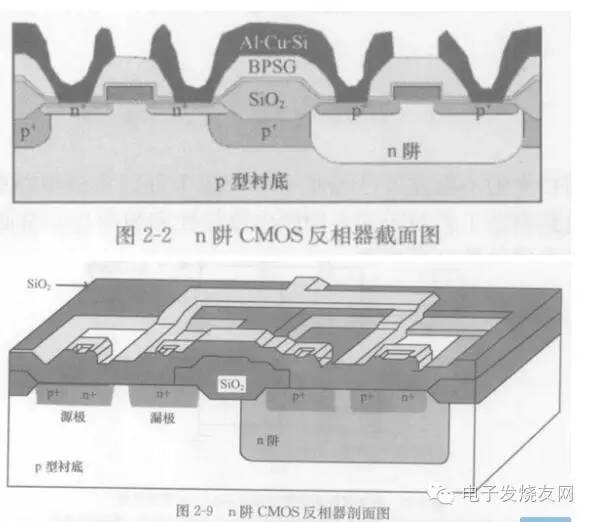

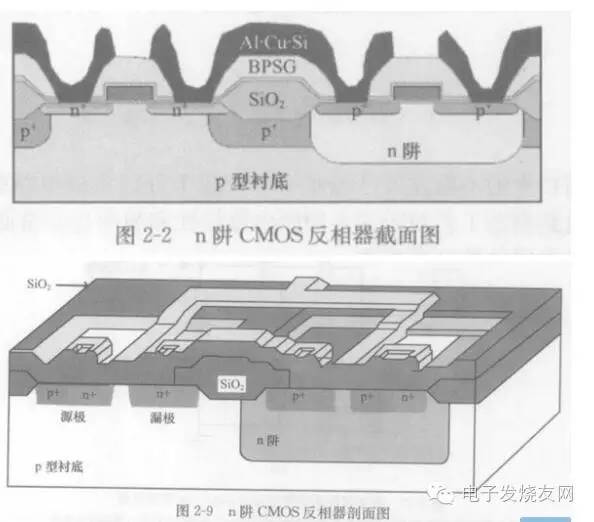

下面兩張圖是p襯底n阱工藝的反相器的截面圖和剖面圖,比其版圖的俯視圖而言,更立體化形象化。

圖7

圖3是一個PMOS管的剖面圖,L就是指兩個有源區之間的距離(源極和漏極之間的距離),當柵(圖中的門級)通低電平時,會在兩個有源區之間的柵的下方形成反型層溝道,這個L就是指的溝道的長度,而源漏的寬度決定了柵下面溝道的寬度,雖然往往管子的寬度比長度在數值上要大,這違背了我們中學的長方形的長與寬的概念,但這里的長指的是溝道的長度,即工藝最小能達到的尺寸。

圖8

到這里看懂了么?沒看懂就翻回去多看幾次。

但有一點需要強調的是,雖然工藝現在已經到了14nm,10nm,7nm甚至有廠商在測試5nm。但這個寬度不會無限的縮小。因為當我們將晶體管縮小到20 納米左右時,就會遇到量子物理中的問題,讓晶體管有漏電的現象,抵銷縮小L 時獲得的效益。

作為改善方式,就是導入FinFET(Tri-Gate)這個概念,如右上圖。在Intel 以前所做的解釋中,可以知道藉由導入這個技術,能減少因物理現象所導致的漏電現象。

圖9

更重要的是,藉由這個方法可以增加Gate 端和下層的接觸面積。在傳統的做法中(左上圖),接觸面只有一個平面,但是采用FinFET(Tri-Gate)這個技術后,接觸面將變成立體,可以輕易的增加接觸面積,這樣就可以在保持一樣的接觸面積下讓Source-Drain 端變得更小,對縮小尺寸有相當大的幫助。

最后,我需要說明一下為什么會有人說各大廠進入10 納米制程將面臨相當嚴峻的挑戰,主因是1 顆原子的大小大約為0.1 納米,在10 納米的情況下,一條線只有不到100顆原子,在制作上相當困難,而且只要有一個原子的缺陷,像是在制作過程中有原子掉出或是有雜質,就會產生不知名的現象,影響產品的良率。

如果無法想像這個難度,可以做個小實驗。在桌上用100 個小珠子排成一個10×10 的正方形,并且剪裁一張紙蓋在珠子上,接著用小刷子把旁邊的的珠子刷掉,最后使他形成一個10×5 的長方形。這樣就可以知道各大廠所面臨到的困境,以及達成這個目標究竟是多么艱巨。

FinFET是什么東西

在前文我們提到,業界為了在縮小制程的同時,減小晶體管的漏電現象,就引入了Finfet的概念。所以我們也有必要先對這個概念進行解析一下。在開始之前,我們先對FET來個解析。

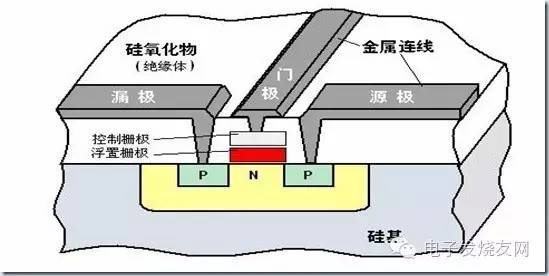

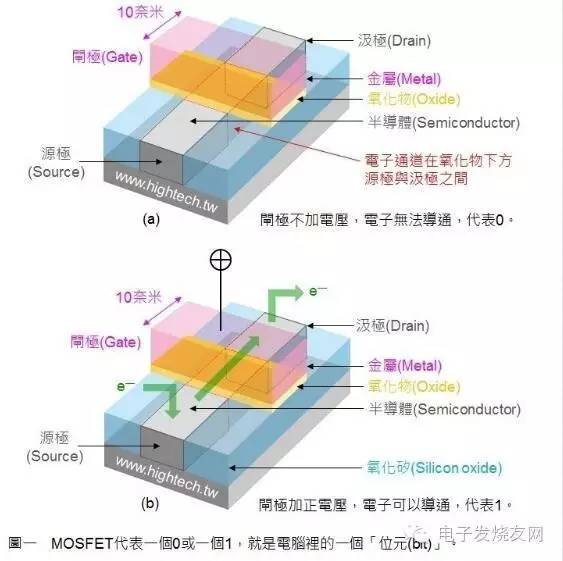

FET的全名是“場效晶體管(Field Effect Transistor,FET)”,先從大家較耳熟能詳的“MOS”來說明。MOS的全名是“金屬-氧化物-半導體場效電晶體(Metal Oxide Semiconductor Field Effect Transistor,MOSFET)”,構造如圖10所示,左邊灰色的區域(硅)叫做“源極(Source)”,右邊灰色的區域(硅)叫做“漏極(Drain)”,中間有塊金屬(紅色)突出來叫做“閘極(Gate)”,閘極下方有一層厚度很薄的氧化物(黃色),因為中間由上而下依序為金屬(Metal)、氧化物(Oxide)、半導體(Semiconductor),因此稱為“MOS”。

圖10

MOSFET 的工作原理很簡單,電子由左邊的源極流入,經過閘極下方的電子信道,由右邊的漏極流出,中間的閘極則可以決定是否讓電子由下方通過,有點像是水龍頭的開關一樣,因此稱為閘;電子是由源極流入,也就是電子的來源,因此稱為源;電子是由漏極流出。

·當閘極不加電壓,電子無法導通,代表這個位是 0,如圖一(a)所示;

·當閘極加正電壓,電子可以導通,代表這個位是 1,如圖一(b)所示。

MOSFET 是目前半導體產業最常使用的一種場效晶體管(FET),科學家將它制作在硅晶圓上,是數字訊號的最小單位,一個 MOSFET 代表一個 0 或一個 1,就是計算機里的一個位(bit)。計算機是以 0 與 1 兩種數字訊號來運算;

我們可以想象在硅芯片上有數十億個 MOSFET,就代表數十億個 0 與 1,再用金屬導線將這數十億個 MOSFET 的源極、汲極、閘極鏈接起來,電子訊號在這數十億個 0 與 1 之間流通就可以交互運算,最后得到使用者想要的加、減、乘、除運算結果,這就是計算機的基本工作原理。晶圓廠像臺積電、聯電,就是在硅晶圓上制作數十億個 MOSFET 的工廠。

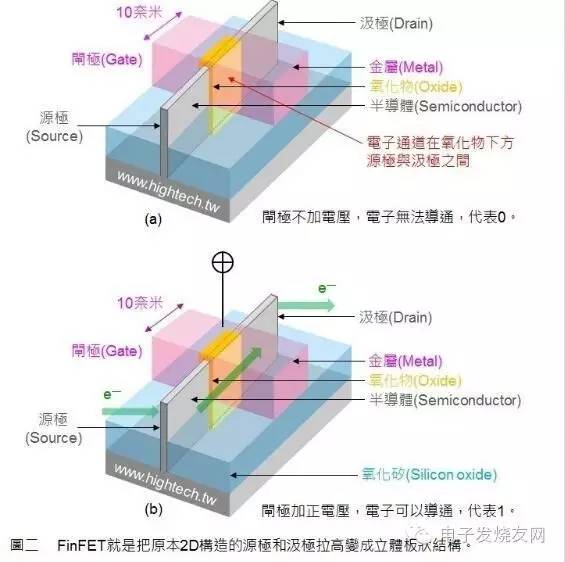

MOSFET 的結構自發明以來,到現在已使用超過 40 年,當閘極長度縮小到 20 奈米以下的時候,遇到了許多問題,其中最麻煩的是當閘極長度愈小,源極和汲極的距離就愈近,閘極下方的氧化物也愈薄,電子有可能偷偷溜過去產生漏電(Leakage);另外一個更麻煩的問題,原本電子是否能由源極流到汲極是由閘極電壓來控制的,但是閘極長度愈小,則閘極與通道之間的接觸面積(圖一紅色虛線區域)愈小,也就是閘極對通道的影響力愈小,要如何才能保持閘極對通道的影響力(接觸面積)呢?

因此美國加州大學伯克萊分校胡正明、 Tsu-Jae King-Liu、Jeffrey Bokor 等三位教授發明了鰭式場效晶體管(Fin Field Effect Transistor,FinFET),把原本 2D 構造的 MOSFET 改為 3D 的 FinFET,如圖11所示,因為構造很像魚鰭 ,因此稱為鰭式(Fin)。

圖11

和傳統的平面型晶體管相比,FinFET器件可以提供更顯著的功耗和性能上的優勢。許多晶圓廠已經上馬16納米或14納米的FinFET工藝。雖然該技術具有巨大的優勢,但也帶來了一些新的設計挑戰,它的成功,將需要大量的研發和整個半導體設計生態系統的深層次合作。

一個挑戰被稱為“寬度量化”,它是因為FinFET元件*好是作為常規結構放置在一個網格。標準單元設計人員可以更改的平面晶體管的寬度,但不能改變鰭的高度或寬度的,所以*好的方式來提高驅動器的強度是增加鰭的個數。增加的個數必須為整數, 添加四分之三的鰭是不允許的。

另一個挑戰來自三維技術本身,因為三維預示著更多的電阻的數目(R)和電容(C)的寄生效應,所以提取和建模也相應困難很多。設計者不能再只是為晶體管的長度和寬度建模,晶體管內的Rs和Cs,包括本地互連,鰭和柵級,對晶體管的行為建模都是至關重要的。還有一個問題是層上的電阻。 20納米的工藝在金屬1層下增加了一個局部互連,其電阻率分布是不均勻的,并且依賴于通孔被放置的位置。另外,上層金屬層和下層金屬層的電阻率差異可能會達到百倍數量級。

另外,由于其自身埋氧化物和絕緣介質較低的導熱性能,使得Finfet自發熱也成為該技術一塊絆腳石。自發熱如果得不到很好的解決,這將對Finfet器件的性能及穩定性等帶來較大的影響。

作為一種新技術與傳統技術相比,傳統MOS管擁有成熟的電路設計技術及規范。然而,FinFET相對傳統MOS器件來講,在電路設計方面,缺少大量的單元庫和IP的支持,這需要未來投資大量人力物力去完善解決。數字設計工程師也會發現新的和更復雜的設計規則,雙圖形著色的要求,和更加嚴格的單元和pin位置的限制。最后,有些SoC設計人員還會被要求來設計和驗證上百萬門級別的芯片。設計師將需要在更高的抽象層次上工作和大量重復使用一些硅IP。

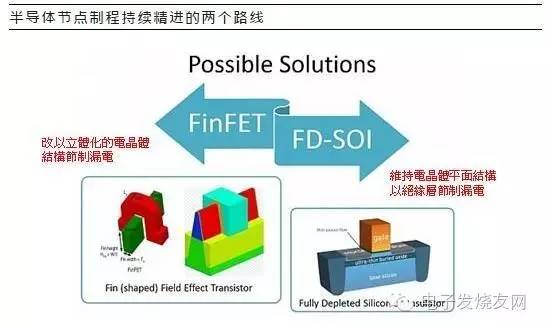

FD-SOI的互補

前面提到了FinFET的出現,解決了很多晶體管面對的一些問題,但在文章末尾也談到了FinFET可能面對的挑戰。于是就有了一個FD-SOI的互補。我們來了解一下。

圖12

FD-SOI,有時也稱Ultra-Thin Body;UTB)制程技術,FD-SOI是一項利用成熟的平面工藝的創新技術,FinFET是一種新的互補式金氧半導體(CMOS)晶體管。兩者都允許晶體管的全耗盡操作,從這點來說兩者相似,相比傳統的bulk技術,在能耗和性能表現方面來說這兩者更加優越。除了復雜性的差異外,完全絕緣的技術在平面上運行有一些優勢。FinFET通過密度更高的晶體管可以帶來稍好的數字性能 ,而FD-SOI也有關鍵優勢:

第*是,晶體管的混合信號性能方面。由于3D晶體管的外形因素,3D結構實際上會構成大型的已開發平面,增加寄生電阻。FD-SOI在混合信號方面主要得益于自然的2D晶體管,由于無摻雜及負偏壓操作能力,其性能甚至超過了傳統的平面bulk CMOS工藝。

第二是,技術成本低。FinFET需要大量的雙重圖形層才能實現微小幾何形的垂直結構。FD-SOI能夠在28nm節點上實現成本平價,同時在更先進的技術節點上進一步優化芯片成本。FD-SOI晶圓作為預處理的晶圓,比bulk silicon價格更貴,隨著更多先進技術的出現和光刻成本的激增,節省的多重光罩成本可以完全抵消FD-SOI基板的預處理成本差額。

第三是,技術研發周期短。FinFET的制造工藝復雜,相比2D晶體管來說,采用3D結構不管是工藝還是設計流程都更難掌控。而FD-SOI簡化了bulk工藝流程,實施起來非常方便,因此研發時間縮短。

國際晶圓廠現狀

現在的晶圓廠有兩種類型:一種是不做上游設計,只做晶圓代工生產的FAB,臺積電、聯電、中芯國際、格羅方德等就是當中的代表;另一種是類似英特爾和三星的IDM,就是覆蓋了從設計到生產到銷售的整個流程。

他們各自的晶圓廠也各有其特點。

全球晶圓廠營收排行

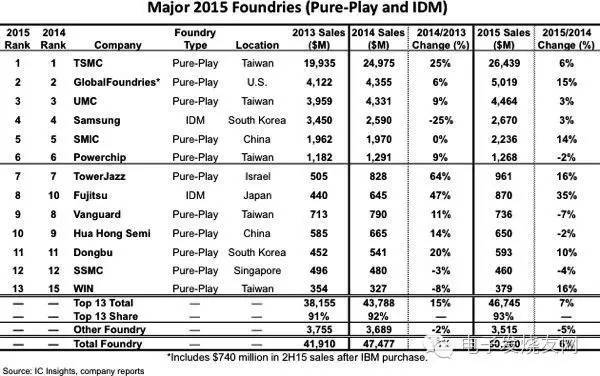

根據IC Insights早前發布的*新一版 2016 McClean Report研究報告,2015年全球晶圓代工廠(包括純晶圓代工服務業者以及IDM廠商的代工業務)排行榜。臺積電(TSMC) 是晶圓代工產業的2015年銷售業績龍頭,去年銷售額達到了264億美元;而臺積電的2015年業績是排名第二的GlobalFoundries之五倍 (就算后者的業績在2015下半年加計了IBM的芯片制造業務),是排名第五的中國晶圓代工業者中芯國際(SMIC)之十二倍。

如 下方圖表所示,在該排行榜上只有兩家是IDM廠(為什么沒有Intel,是因為他們沒單獨做統計么?求解析!),包括三星(Samsung)與富士通(Fujitsu),因為IBM與韓國業者Magnachip已經跌 出排行榜之外;而盡管流失大部分來自蘋果(Apple)的業績,三星仍然是2015年IDM廠商晶圓代工業務龍頭,其業績是富士通的三倍。

要 說明匯率波動對IC產業銷售額的劇烈影響,從臺積電的2015年成長率可見一斑──該公司的年度成長率為6%,是其所在地貨幣成長率(11%)的一半左 右,因此雖然該公司年度業績以臺幣計算(新臺幣8,405億元)的成長率有達到10%目標、甚至更佳,但是換算成美元后成長率僅剩6%。

從 臺積電的業績也可看出Apple訂單有多么重要──該公司去年的晶圓代工業績成長了1.464億美元,而來自Apple的業績則增加了1.990億美元, 超過了臺積電2015年晶圓代工業績增加金額的100%,因此若沒有Apple,臺積電去年的晶圓代工業績會衰退2%,比該公司實際成長率6%減少了8個 百分點。

圖13· 2015年全球晶圓代工業者排行榜(包括純晶圓代工服務業者以及IDM廠的晶圓代工業務)

全球晶圓代工業績排名第二的GlobalFoundries,在2015年7月初合并了IBM的IC業務;在此要注意的是,除了IBM在2014年創造的5.15億美元的IDM晶圓代工業績,該公司在該年度還有約10億美元的IC營收內部轉移。

因 此GlobalFoundries的2015年第四季銷售業績為14億美元左右,年度營收運轉率(annual run-rate)為56億美元,約比該公司2015年銷售額50億美元高出12%。若不加計下半年并入的IBM業績,GlobalFoundries的 2015年銷售額衰退2%。

在上方圖表所顯示的2015年全球前十三大晶圓代工業者的總營收為467億美元,占據年度整體晶圓代工產業銷售額503億美元的93%,比兩年前2013年時的91%多了2%。隨著晶圓代工產業進入門坎越來越高,IC Insights預期此比例隨來還將繼續增加。

知名晶圓廠的*新工藝進展

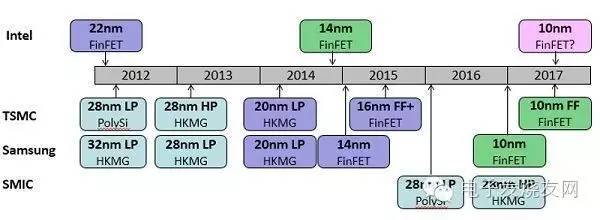

在摩爾定律的推動下,半導體工藝制程也在快速推進,具體就表現在TSMC、三星和Intel這幾個領頭羊身上。我們來看一下他們各自的工藝進展。

大體進展

2015年Intel、三星、TSMC都已量產16/14nm FinFET工藝,下一個節點是明年的10nm,而10nm之后的半導體制造工藝公認越來越復雜,難度越來越高,甚至可能讓摩爾定律失效,需要廠商拿出更多投資研發新技術新材料。

TSMC在FinFET工藝量產上落后于Intel、三星,不過他們在10nm及之后的工藝上很自信,2020年就會量產5nm工藝,還會用上EUV光刻工藝。

TSMC日前舉行股東會議,雖然董事長張忠謀并沒有出席,不過兩大聯席CEO劉德音、魏哲家及CFO何麗梅都出席了會議,公布了TSMC公司Q2季度運營及技術發展情況,該公司調高了今年的資本支出到95-105億美元,高于Intel公司的90-100億美元,顯示對未來發展的看好。

至于工藝進展,劉德音公布了TSMC的2020路線圖,認為EUV光刻工藝在2020年時能有效降低量產5nm工藝的成本,TSMC計劃在5nm節點上應用EUV工藝以提高密度、簡化工藝并降低成本。

目前TSMC公司已經在7nm節點研發上使用了EUV工藝,實現了EUV掃描機、光罩及印刷的工藝集成。TSMC表示目前他們有4臺ASML公司的NX:3400光刻機在運行,2017年Q1季度還會再購買2臺。

之前有報道稱三星也購買了ASML公司的量產型EUV光刻機,目的是在2017年加速7nm工藝量產。

EUV是新一代半導體工藝突破的關鍵,但進展一直比較緩慢,至少比三星、TSMC兩家的嘴炮慢得多——早前TSMC宣稱在2016年的10nm節點就能用上EUV工藝,之后又說7nm節點量產EUV工藝,但現實情況并沒有這么樂觀,現在他們的說法也是2020年的5nm節點,跟Intel的預計差不多了。

5nm還很遙遠,10nm及7nm還比較現實,TSMC表示他們的10nm工藝已經有三個客戶完成流片,雖然沒公布客戶名稱,但用得起10nm工藝的芯片也就是蘋果A10、聯發科X30(被海思、展訊刺激的聯發科在X30上爆發了)以及海思新一代麒麟處理器,流片的估計就是這三家了。

TSMC表示今年底之前還會有更多客戶的10nm芯片流片,該工藝將在2017年Q1季度量產。

至于7nm,TSMC表示他們已經提前256Mb SRAM芯片,進展順利,CEO表示相信TSMC的7nm工藝在PPA密度、功耗及性能方面要比對手更出色,已經有高性能客戶預計在2017年上半年流片,正式量產則是在2018年。

專家分析

市場研究機構Linley Group首席分析師Linley Gwennap也表示,英特爾(Intel)將在10nm工藝優于臺積電(TSMC)與三星(Samsung),就像在14nm時一樣。VLSI Research首席執行官G. Dan Hutcheson認為,臺積電即將量產的10nm工藝將大幅超越英特爾的14nm節點,而且臺積電正以較英特爾更快的速度超前進展。此 外,International Business Strategies (IBS)創辦人兼首席執行官Handel Jones則指出,英特爾與臺積電的10nm工藝技術性能旗鼓相當。

但各方均同意,有多種變量決定了組件如何制造,對于不同類型芯片的影響也各不相同。分析師們還把責任歸咎于營銷部門,認為他們經常是讓情況變得更加模糊,而非厘清現實。

“事實上,沒有一種衡量方式能夠決定一項技術的性能、功耗與晶體管密度,”Jones說,“金屬層M1間距十分重要,但局部互連也會影響到布線的閘極密度與性能;閘極間距對于閘極密度相當重要,但鰭片高度也明顯影響性能。”

“互連延遲正成為重大的挑戰,尤其是在10nm時有80%的性能都取決于互連延遲的影響,”他補充說。

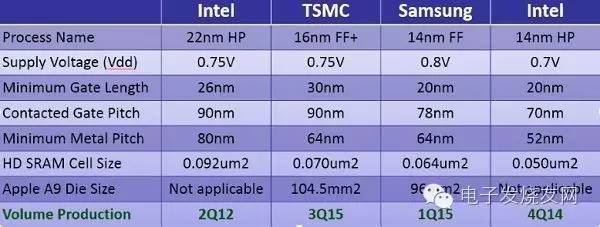

從Linley Group的衡量指標來看,英特爾比臺積電和三星更具優勢

FinFET的高度與線寬可作為衡量技術節點與芯片制造商實力的良好指針。Hutcheson認同這一觀點,他并表示,SRAM的單元尺寸也值得考慮。

但是,“我認為技術進展的終極衡量標準在于隨著每一技術節點倍增密度的能力,”Hutcheson說,“英特爾至今在每一節點都達到了這一目標。”

也就是說,臺積電在10nm達到的M1金屬層間距已能“完整微縮(~70%),領先英特爾的14nm,”Hutcheson強調,英特爾持續14nm節點也已經2年了。

隨著近期披露10nm與7nm計劃,“臺積電不僅證明擁有扳回勝局的魔力,同時還踩著比任何人更快的進展步調,”他補充說。

同時,盡管在今年1月,一些業者還不那么看好其16/14 nm節點,但臺積電目前的16nm節點“在相同的時間架構下,已經在營收與良率方面雙雙超越了28nm,”他強調。

節點性能與名稱無關?

Gwennap表示,技術節點的傳統衡量標準是晶體管尺寸,亦即所測得的最小閘極長度。然而,歸功于市場營銷的努力,如今的節點名稱不再與閘極測量結果吻合了,“但其差距也不算太大——英特爾14nm工藝的閘極長度約相當于三星(Samsung)的20nm。”

不過,Gwennap說,臺積電和三星目前“在速度與密度方面都遠落后英特爾的14nm工藝,”以此來看,他認為三星的節點更適合稱為17nm,臺積電則為19nm。“預計在10nm時的情況類似…三星與臺積電將在速度與密度方面落后英特爾約一至半個節點。”

然 而,光是最小閘極長度并不足以決定一切,Chipworks*深研究員兼技術分析師Andy Wei表示,“定調一項技術是否最優,高度取決于與面積微縮有關的工藝成本。而這可歸結為比較布線單元級的技術能力,以及達到該密度所需的成本,Chipworks正是以此作為基準”。

Linley Group認為,三星可望最先推出10nm工藝,但英特爾的表現會更優

自從德州儀器(TI)為了如何衡量閘極長度而戰,工藝節點的命名之爭已經持續25年了。Hutcheson說,TI采用有效閘極長度,而硅谷芯片制造商則以更大的閘極長度作為指標。

在1990年代,當線寬微縮至納米級時,“新的論據認為閘極長度不再適用,因為蝕刻削薄而使M1金屬級間距成為更適合的標準——不過卻仍由閘極長度決定性能。”

其后,臺積電宣稱其40nm工藝比英特爾使用的45nm節點更好,但除了“更好”似乎也沒提出任何指標,Hutcheson指出,“從那時起,就一直有點像 是‘各自表述’一樣。例如,Globalfoundries的32nm和28nm之間真正的差異是32nm是SOI工藝,28nm則是bulk工藝。”

臺積電已經明確表示其16nm工藝采用20nm的后段工藝技術——FinFET晶體管層迭于頂部。在最近于圣荷西舉行的會議,臺積電表示,其7nm節點將會 較其10nm工藝密度更高1.63倍,Chipworks的Wei說,“這使得2種尺寸微縮0.7倍的性能提高還不到2倍,而節點名稱微縮了0.7倍。”

“市場營銷元素強烈影響節點的命名,而且著眼于頂級規格,但設計工程師知道他們所選擇的技術優點,”Jones表示。畢竟,“只要工藝技術快速、低功耗且低成本,那么怎么稱呼都不重要。”

來源:電子發燒友

陜公網安備 61019002000416號

陜公網安備 61019002000416號

業務咨詢

業務咨詢